# Automated Robustness Verification of Concurrent Data Structure Libraries against Relaxed Memory Models

**Extended Version**

KARTIK NAGAR, IIT Madras, India ANMOL SAHOO, Purdue University, USA ROMIT ROY CHOWDHURY, Chennai Mathematical Institute, India SURESH JAGANNATHAN, Purdue University, USA

Clients reason about the behavior of concurrent data structure libraries such as sets, queues, or stacks using specifications that capture well-understood correctness conditions, such as linearizability. The implementation of these libraries, however, focused as they are on performance, may additionally exploit relaxed memory behavior allowed by the language or underlying hardware that weaken the strong ordering and visibility constraints on shared-memory accesses that would otherwise be imposed by a sequentially consistent (SC) memory model. As an alternative to developing new specification and verification mechanisms for reasoning about libraries under relaxed memory model, we instead consider the orthogonal problem of library robustness, a property that holds when all possible behaviors of a library implementation under relaxed memory model are also possible under SC. In this paper, we develop a new automated technique for verifying robustness of library implementations in the context of a C11-style memory model. This task is challenging because a most-general client may invoke an unbounded number of concurrently executing library operations that can manipulate an unbounded number of shared locations. We establish a novel inductive technique for verifying library robustness that leverages prior work on the robustness problem for the C11 memory model based on the search for a non-robustness witness under SC executions. We crucially rely on the fact that this search is carried out over SC executions, and use high-level SC specifications (including linearizability) of the library to verify the absence of a non-robustness witness. Our technique is compositional - we show how we can safely preserve robustness of multiple interacting library implementations and clients using additional SC fences to guarantee robustness of entire executions. Experimental results on a number of complex realistic library implementations demonstrate the feasibility of our approach.

Additional Key Words and Phrases: Relaxed Memory Models, Concurrent Library implementations, Robustness

## 1 Introduction

Unlike a sequentially consistent (SC) [41] memory model where concurrently executing threads all witness the same view of memory, relaxed memory models such as those found in C11 [7, 8, 15] allow each thread to have its own logical view of memory, resulting in behaviors like store buffering that are not expressible under SC [37]. A program written to take advantage of the performance benefits afforded by executing under a relaxed memory model M, but whose behaviors can nonetheless be fully explained in terms of SC (interleaved) executions, is said to be *robust* against M. Intuitively, a robust program is one in which every relaxed memory execution is also an SC one.

In this paper, we consider the problem of *automatically* verifying the robustness of library implementations against RC20 [43], a useful variant of the C11 memory model. C11 allows the expression of high-performance concurrent C/C++ code through the use of annotations affixed to memory accesses. Release (rel) and acquire (acq) annotations enable a form of message-passing between "release" writes and "acquire" reads [38], yielding a causally-consistent ordering between

Authors' Contact Information: Kartik Nagar, IIT Madras, Chennai, India, nagark@cse.iitm.ac.in; Anmol Sahoo, Purdue University, West Lafayette, USA, sahoo9@purdue.edu; Romit Roy Chowdhury, Chennai Mathematical Institute, Chennai, India, romit@cmi.ac.in; Suresh Jagannathan, Purdue University, West Lafayette, USA, suresh@cs.purdue.edu.

2024. ACM 2475-1421/2024/10-ART362 https://doi.org/10.1145/3689802 the operations that precede the "release" and those that follow the "acquire"; and, relaxed (r1x) annotations are used to compile accesses to single hardware loads and stores with no additional synchronization, other than basic store coherence guarantees [33] provided by the hardware. RC20 provides an improved semantics for atomic accesses [40], prevents undesirable executions involving out-of-thin-air reads, and simplifies the semantics of synchronization for release-acquire pairs.

Robustness under the RC20 memory model is a well-studied problem [38, 43] for which algorithms to check robustness of finite-state programs operating over a bounded number of threads have been developed. By showing a program to be robust, one can then reason about its correctness w.r.t. a high-level specification under the SC memory model, which is a significantly simpler problem. Consequently, any correctness guarantees proven under SC also continue to hold under RC20. Thus, proving library robustness can also enable a similar pathway to reasoning about correctness of programs using library implementations under RC20. Prior efforts addressing the correctness of library implementations under relaxed memory models have mostly focused on developing newer forms of specification [18, 44, 49, 52] that allows reasonable non-SC behaviors and also exposes the internals of the underlying memory model. While these specifications can admit highly efficient library implementations, proving their correctness requires significant manual effort because of the need to closely correlate abstract state-based specifications with the event-based relaxed memory model semantics. Furthermore, using these relaxed specifications to prove correctness of client programs using the library implementation is also highly non-trivial. On the other hand, by proving a library implementation to be robust in the context of the most general client, we can extend this robustness guarantee to any client program using the library, thus allowing one to reason about its correctness under SC, which is a well-studied problem.

Following the classical modular verification paradigm, we would like to separately verify the robustness of library implementations and their clients and then compose these guarantees together to establish robustness of the overall execution. We consider the following strategy: first verify a library implementation to be robust in the presence of a most general client, which can call the library methods an arbitrary number of times across an arbitrary number of threads, and then use this robustness guarantee to prove the robustness of any client program potentially calling multiple libraries. Clearly, if a library is not robust on its own, any client program using the library (and which does not restrict the concurrent behaviors of the library) would also be non-robust.

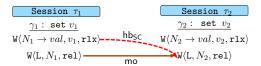

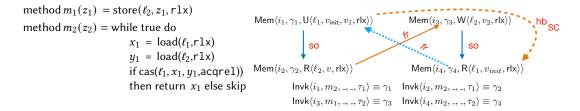

Unfortunately, we find that naïvely composing individually robust libraries may not lead to an overall robust execution. To illustrate this, consider the two simple register libraries  $\mathcal{L}_1$ and  $\mathcal{L}_2$  given in Fig. 1. It is well known that under the RC20 memory model, atomic accesses to a single location follow SC-per-location semantics, and thus both the libraries (which access

Fig. 1. Example showing non-compositionality of robustness

single distinct locations  $\ell_1$  and  $\ell_2$ ) will be individually robust for the most general client. However, we can construct a standard store-buffering execution formed out of interaction with both libraries, as shown by the sessions  $\tau_1$  and  $\tau_2$  in the figure (assume that the initial value at locations  $\ell_1$  and  $t_2$  is 0). This execution is not possible under SC, because in any interleaving, at least one of set 1 or set2 (and hence the underlying store) operations will happen first, so that at least one of the get1 or get2 operations would return 1. To recover overall robustness, we can add an SC-fence when crossing libraries within every session. In the RC20 memory model, an SC-fence is defined using a composition of three instructions: fence(acq); fadd(f, 0, acqrel); fence(rel) where f is

an identifier for a distinguished location not accessed by any other instruction [43]. The fadd instruction guarantees synchronization between any two SC fences.

In the execution above, suppose we place an SC fence between the two invocations in each session. Then, the total ordering among the fences would prevent both the loads from ignoring the stores under RC20, thus prohibiting the store buffering anomaly. On the other hand, if even one of the SC-fences is removed, store buffering is still possible. We call an execution *well-fenced* if there is an SC-fence between every adjacent pair of invocations to different libraries in every session.

Having well-fenced executions then gives us a way to decompose the overall robustness problem into robustness of individual libraries. In this work, we leverage this observation and make significant progress on the problem of verifying robustness of programs using library implementations: (i) we propose an automated, sound (but not complete) verification procedure for proving robustness of individual library implementations against the most general client, (ii) we formally prove that a well-fenced execution comprising of calls to individually robust libraries is guaranteed to be robust.

Verifying individual library robustness conceptually requires us to compare the set of all SC and RC20 executions of the library implementation. This is a non-trivial problem because the most general client can invoke library methods an arbitrary number of times concurrently across an arbitrary number of threads. Previous efforts on robustness verification of relaxed memory programs [11, 38, 43] are only applicable for finite state programs involving a bounded number of threads. Our primary contribution in this regard is a fully automated verification strategy that is not constrained by these restrictions.

Our verification strategy is based on searching SC executions of a library implementation for potential *non-robustness witnesses* [38, 43]. SC executions are constructed by simply treating all memory accesses as being sequentially consistent, ignoring the actual annotations affixed to these accesses in the program. A non-robustness witness is a prefix of an SC execution that contains a location whose latest write *w* would be witnessed by the next operation (say a read *r*) in that execution, but which may not necessarily be witnessed in an RC20 execution, i.e. informally,  $hb_{SC}(w, r)$  holds but  $hb_{RC20}(w, r)$  does not, where  $hb_{SC}$  and  $hb_{RC20}$  define a happens-before ordering among read and write actions in SC and RC20 executions, resp. Verifying the absence of such a witness is tantamount to showing robustness in a RC20 setting [38, 43]. We use an inductive strategy to cover the infinite set of executions, and crucially take advantage of axioms and constraints provided by the library's SC specification to help discharge the verification conditions.

We note that unlike prior approaches to robustness verification [38, 43] which are both sound and complete, our approach sacrifices completeness for the sake of automation by devising sufficient but not necessary conditions for proving absence of a non-robustness witness. However, this makes our verification strategy more amenable to automation, and also better suited to library implementations. We also crucially rely on expressive SC specifications to rule out infeasible non-robustness witnesses, with the caveat that spurious non-robustness witnesses can arise if the SC specification is not expressive enough. However, our extensive experimental evaluation suggests that the SC specification of the standard data structures is rich enough to verify a number of complex implementations.

This paper makes the following contributions:

(1) We provide a verification methodology for proving robustness of a concurrent data structure library executing under the RC20 memory model. To enable automated verification, our proof methodology exploits various constraints derived from the library's SC specification. We provide a common SMT-based framework to systematically relate these high-level constraints with the low-level event-based guarantees required for robustness proofs.

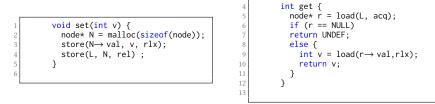

Fig. 2. A stylized C11 implementation of a Register library. The contents of variables N and L can be accessed by multiple threads; variable r, on the other hand, is thread-local.

- (2) We introduce a new notion of robustness, called *induced subgraph robustness*, tailored for reasoning about robustness of library implementations that may have benign non-robustness as part of their speculative computations. This weaker definition permits executions to have library-internal non-robust operations, as long as their effects do not manifest in a method's return value.

- (3) We extend our methodology for proving robustness of an individual library to compose multiple robust libraries using SC fences to guarantee overall execution robustness. Our composition guarantees also extend to induced subgraph robustness. Our initial experiments indicate that the performance penalty of putting additional SC fences is not significant, and potentially masked by the synchronization already performed by the individual libraries to maintain robustness.

- (4) We have applied our approach on a number of realistic concurrent C11 library implementations, including real-world benchmarks such as Meta's Folly lock-free queue implementation that make sophisticated use of relaxed atomics [26]. Our results establish, often for the first time, robustness against RC20 of well-known library implementations.

The remainder of the paper is structured as follows. The next section presents a motivating example to illustrate the core ideas underlying our approach for proving robustness of a library. §3 introduces a representative language, along with an axiomatic formalization of the memory model. The derivation of the inductive invariant used for our robustness proof is given in §4. We formalize the definition of induced subgraph robustness in §5. We provide our methodology to compose robust libraries in §6. Details about the implementation and SMT encoding are given in §7. Experimental results are presented in §8. Related work and conclusions are given in §9.

## 2 Motivating Example

Consider an implementation of a concurrent register data structure shown in Figure 2. Although not very efficient, it nonetheless exhibits access patterns commonly found in a number of real-world library implementations, and it allows us to provide a simple, concise demonstration of the core ideas of our verification strategy. The register data structure has two methods (set(v) and get), with the intended semantics that get returns the most recent value that was assigned to the register by a set operation, or else UNDEF if no set operations have yet executed. In Figure 2, the set method is implemented by allocating a new node containing the value (in the field val), storing a reference to the node in a shared variable L. The get method reads the variable L and then derefences the val field (if L is not NULL) to return the value. Notice that each memory access is annotated with an access mode, which has an effect on its behavior, as well as the behavior of subsequent accesses.

If we ignore the annotations defining relaxed access modes and assume all reads and writes to shared-memory are SC, then every concurrent execution can be thought of as an interleaving of

statements from different threads, all accessing a single shared memory. Under SC, it is straightforward to prove that the above implementation is correct, which means that all the invocations in an execution follow the intended register semantics.

## 2.1 RC20 Memory Model and Robustness

In order to describe executions under the RC20 relaxed memory model, we consider the read/write events generated during an execution, as well as dependency relations between these events. In the following, we give a brief informal description of these relations; they are formally defined in the next section. The relations include (i) *reads-from* (rf) that relates a write event to the read event which reads from it, (ii) *modification-order* (mo), a total ordering on all write events to the same location, and (iii) *from-read* (fr), a relation that relates a read event to write events that occur later than the write event it reads from according to the mo order. Events in the same thread are all totally ordered according to a session order (so) relation, a generalization of program order adapted to a concurrent library setting (a session is defined as a sequence of library method invocations performed by the same thread).

The access modes associated with read/write events are used to determine the *synchronizes-with* relation (sw): write and read events that are related by rf are also related by sw if the write is annotated with rel access mode and the read is annotated with acq mode (there are also other ways to establish sw, more details in §3.2). Finally, these primitive relations are used to define two derived relations: (i)  $hb_{SC}$ , the transitive closure of rf, fr, mo, so, and (ii) hb, the transitive closure of sw and so. Intuitively,  $hb_{SC}$  will be used to define the behavior of SC executions, while hb will define the behavior of RC20 executions.

For the purpose of this section, we are mainly interested in how the RC20 memory model uses hb to constrain the behavior of read events by forcing them to not ignore write events that are in hb order to them. This means that a read event  $e_r$  cannot read from a write event  $e_w$  if there is another write event  $e'_w$  such that  $e_w \xrightarrow{\text{mo}} e'_w$  and  $e'_w \xrightarrow{\text{hb}} e_r$  (more precisely,  $e'_w$  must be in hb-order before some previous event in the session containing  $e_r$ ). In this case,  $e_r$  must read from either  $e'_w$ or an event mo-after  $e'_w$ .

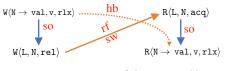

To illustrate this, consider an execution of the register library consisting of two invocations, set(v)and get. The events generated during this execution are shown in Figure 3, with the two events on the left side of the figure generated by set(v) and the two events on the right generated by get. Assuming that the malloc statement in set(v) allocates a new

Fig. 3. An execution of the register library

node N, the rf relation from the store of L in set to the load of L in get induces a sw relation (because of the rel and acq annotations associated with the store operation in the set method (line 4) and the load operation in the get method (line 5)). Due to this, the write of  $N \rightarrow val$  in set comes in hb-order before the read of  $N \rightarrow val$  in get. As a result, this load must read the value v. However, if the access mode of either the load or store to L are changed to rlx, then the store to  $N \rightarrow val$  would no longer be in hb order, allowing the load to  $N \rightarrow val$  to ignore it. The execution in Figure 3 corresponds to classical message-passing behavior, and is possible under both SC and RC20.

The robustness problem then asks whether any arbitrary RC20 execution of the library implementation is also possible under SC. In order to solve the robustness problem, we consider an alternative event-based characterization of SC executions: SC constrains the behavior of read events by forcing them to not ignore write events which are in hb<sub>SC</sub> order before them. This characterization is almost

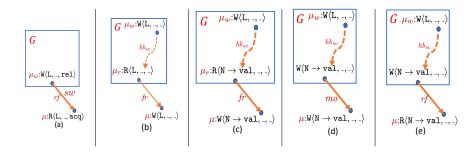

Fig. 4. Establishing the inductive invariant for the location L in the register library implementation

identical to the RC20 memory model, replacing the hb relation with hb<sub>SC</sub>, and this observation leads to the following sufficient condition for robustness[43]: At every step during an SC execution, if the next event is a read event  $e_r$  to location  $\ell$ , and if the most recent write event  $e_w$  to  $\ell$  (according to the mo ordering) is in hb<sub>SC</sub> order to the session  $\tau$  containing  $e_r$ , then  $e_w$  is also in hb ordering to  $\tau$ . This means that, under RC20, the read event  $e_r$  cannot ignore the write event  $e_w$ , and hence it must have the same behavior as under SC. Notice that although we are trying to establish robustness of RC20 executions, the robustness condition itself needs to be checked over SC executions only. This is because we are essentially searching for the minimal or first robustness violation, and hence the execution leading up to the violation must be itself robust and hence possible under SC.

Coming back to the execution in Figure 3, just before the event  $R\langle N \rightarrow val, v, rlx \rangle$ , the most recent write event to the location  $N \rightarrow val$ ,  $W\langle N \rightarrow val, v, rlx \rangle$ , is in both  $hb_{SC}$  and hb order, thus ensuring that the read event has the same behavior under both SC and RC20. On the other hand, if the access modes of either the load or store to L were to be changed to rlx, robustness would be violated by the read event to  $N \rightarrow val$ , resulting in a manifestation of a non-robustness witness.

#### 2.2 Verifying Robustness

Our verification strategy aims to prove the absence of non-robustness witnesses, which are nothing but violations of the sufficient condition for robustness: an SC execution of the library implementation that contains a write event on a location  $\ell$  that is in hb<sub>SC</sub> but not hb order to a session where the next event is a read event on  $\ell$ . Since a library implementation can be invoked an arbitrary number of times by clients across arbitrary number of threads, we have to reason about robustness of an unbounded number of executions. To make this problem tractable, we define an inductive proof strategy that essentially uses the absence of non-robustness witnesses as an inductive invariant. We prove the correctness of the inductive invariant systematically on a per-location basis, and use information about the SC behavior of the library implementation (such as its high-level specification under SC) to facilitate automated verification.

To illustrate, we describe how to verify the robustness of the register implementation of Figure 2. Executions of this implementation access two classes of locations: (i) L and (ii) N $\rightarrow$ val for different values of N. We reason about the absence of non-robustness witnesses involving these location classes separately. Intuitively, the rel/acq annotations to the store/load of location L should ensure robust behavior of loads to location N  $\rightarrow$  val. However, it is not clear how the implementation ensures robustness for accesses to location L. We prove that it does so by establishing the following inductive invariant over all SC executions: *if the most recent write to the location* L (according to mo) comes hb<sub>SC</sub> before another event, then it also comes hb before it. This would then ensure that a subsequent load to L would have the same behavior under SC and RC20. We use induction on the

number of events in an SC execution, and consider adding events in an order that obeys the hb<sub>SC</sub> relation. Figure 4 depicts some of the more interesting inductive cases; for each case, we consider an arbitrary SC execution *G* of the library (depicted by the rectangle) and a new event  $\mu$  to be added to the execution. The most recent write to location L in the execution *G* is labelled  $\mu_w$ . Inductively, we assume that if  $\mu_w$  comes hb<sub>SC</sub> before another event in *G*, it also comes hb before it.

The various cases exhaustively consider new additions to  $hb_{SC}$  due to the inclusion of  $\mu$ . We highlight the different ways in which the inductive invariant is maintained. Figure 4(a) considers the case where  $\mu$  is a read event to L, which can cause a new  $hb_{SC}$  edge to be established through the rf relation. Now, since all writes to L use the access mode rel while all reads to L use access mode acq, the rf relation induces a sw relation, and thus a hb relation so that the required condition continues to hold. Figure 4(b) depicts an execution in which  $\mu$  is a write to L that results in an incoming fr edge from an existing read ( $\mu_r$ ) in *G*. Note that the dotted arrow labeled with  $hb_{SC}$  indicates that the  $hb_{SC}$  relation is established through some sequence of events. Now, since  $\mu_w$  occurs  $hb_{SC}$ -before  $\mu_r$ , it also occurs  $hb_{SC}$ -before  $\mu$ . However, in the new execution after addition of the event  $\mu$ , notice that  $\mu$  now becomes the most recent write to L, and it cannot occur  $hb_{SC}$  before any event in *G* (because we are adding events in  $hb_{SC}$  order). Hence, the required invariant holds trivially, and we do not have to consider any  $hb_{SC}$  paths from  $\mu_w$ .

A more interesting case is shown in Figure 4(c). Here  $\mu$  is a write event to N→val and its addition to the execution establishes a new hb<sub>SC</sub> path from  $\mu_w$  through a fr relation on  $\mu_r$ . On the surface, it would seem that this depicts a non-hb (but hb<sub>SC</sub>) path from  $\mu_w$  to  $\mu$ . However, in an actual execution, the fr relation involving N→val can never arise. In the following, we show how we can infer the infeasibility of this execution by using the fact that we are only considering SC executions.

Notice that in a SC execution, there is a unique write to any location of the class  $N \rightarrow val$ , because it only happens inside the set method, and malloc will always return a fresh location. Since  $\mu_r$ does not read from this write event, and since there is no other write event to  $N \rightarrow val$ ,  $\mu_r$  must read the initial value of the location (say 0), which will also be returned by get invocation containing  $\mu_r$ . However, the register implementation is agnostic to the actual value passed as an argument to set (i.e., set's control-flow is unaffected by v) and thus we can assume data independence of its arguments [1]. In particular, we prohibit executions where set is passed the initialization value 0. But the get invocation containing  $\mu_r$  returns 0, and the register specification says that for every get invocation which return a non-UNDEF value, there must be a set invocation whose argument value is the same as the return value of the get invocation. We thus derive a contradiction, establishing infeasibility of the execution in Fig. 4(c). Notice how we are able to leverage program structure constraints (uniqueness of write to  $N \rightarrow val$  enforced by malloc) and the register specification for this reasoning.

The cases depicted in Figures 4(d) and 4(e) can also be handled in a fashion similar to the handling of cases 4(a) - 4(c). In particular, the execution shown in Figure 4(d) is not possible due to uniqueness of writes to N $\rightarrow$ val. Figure 4(e) depicts a feasible execution. In this case, there will already exist a hb ordering between the event W(N $\rightarrow$ val, \_, \_) and  $\mu$  (as shown in Figure 3) via a path comprising sw and so edges. Using the inductive hypothesis that  $\mu_w$  also occurs hb-before W(N $\rightarrow$ val, \_, \_) and the transitivity of hb, we can infer that  $\mu_w$  occurs hb-before  $\mu$ . Collectively, our case analysis shows robustness for the location L, guaranteeing that there can be no non-robustness witnesses caused by accesses to this location. In each case, either we cannot establish the hb<sub>SC</sub> relation, or if we can, then hb relation is also established. A similar analysis can be carried out for the location N $\rightarrow$ val.

The following sections formalize these intuitions, generalizes the approach to deal with implementations that use loops and synchronization operations like cas and fence, and builds an automated procedure to perform the above reasoning. Kartik Nagar, Anmol Sahoo, Romit Roy Chowdhury, and Suresh Jagannathan

```

v \in Value ::= c \mid \ell

e \in \mathsf{Expr} ::= v \mid x \mid e1 == e2 \mid \dots

c \in Constant

I \in Method ::= method m(x) = s

\ell \in Location

x, y \in Var

s \in Stmt ::= skip | x = e | x = malloc(c)

\tau \in SessionId

| store(x, e, o_{W}) | y = load(x, o_{R}) | y = cas(x, e_{1}, e_{2}, o_{U}, o_{R}) | fence(o_{F})

m \in MethodName

| y = fadd(x, e, o_U) | s_1; s_2 | if e then s_1 else s_2 | while e do s | return e

\mu \in MemEvt

o_{X} \in Mod_{X} where X \in \{R, W, U, F\}

\alpha \in \text{Action} ::= \epsilon \mid \mathsf{R}\langle \ell, v, o_{\mathsf{R}} \rangle \mid \mathsf{W}\langle \ell, v, o_{\mathsf{W}} \rangle \mid \mathsf{U}\langle \ell, v_1, v_2, o_{\mathsf{U}} \rangle \mid \mathsf{F}\langle o_{\mathsf{F}} \rangle

\gamma \in \text{InvkEvt} ::= \text{Invk}\langle i, m, v_a, v_r, \tau \rangle

\omega \in \text{Evt} ::= \gamma | \text{Sil}\langle \gamma \rangle | \text{Mem}\langle i, \tau, \alpha \rangle

```

Fig. 5. Domains and language syntax.

#### 3 Preliminaries

## 3.1 Syntax and Program Semantics

To describe our approach, we consider a C-style imperative language, with standard control-flow operators (sequencing (;), while, if-then-else, etc.), and operations to access thread-local and shared state (Figure 5). A library implementation of a data structure is given by a set of methods written in this language, with each method corresponding to an operation of the data structure; we prohibit methods from invoking other methods.

Library implementations have access to a shared heap i.e., an unbounded collection of locations (Location), shared among all sessions; additionally, library methods can bind and read local variables whose values are accessible to the method only for the lifetime of the invocation. We assume that every instance of the malloc(c) command returns a unique location on the heap, allocating c units of memory. We also require that a library implementation owns its accessed locations, which means they cannot be accessed by clients (or other library implementations) [49]. A method body is a sequence of statements, at least one of which must be a return.

The most interesting part of the language are statements that access shared memory. Specifically, statements  $load(x,o_R)$  and store $(x,e,o_W)$  are used to load values from, and store values to, locations in shared memory whose address is contained in variable x, resp. Following the RC20 memory model, each shared memory access in our language is also associated with an *access mode*, taken from the set Mod  $\triangleq$  {rlx, acq, rel, acqrel}. These modes define the consistency level of the memory access. Note that the language does not allow non-atomics, as every access is identified with a consistency level. We define specific subsets of access modes for the different types of memory accesses:

| $Mod_{R} = \{rlx, acq\}$ | $Mod_U = \{rlx, acq, rel, acqrel\}$ |

|--------------------------|-------------------------------------|

| $Mod_W = \{rlx, rel\}$   | $Mod_F = \{acq, rel, acqrel\}$      |

A partial order  $\sqsubseteq$  is also defined over these access modes, which intuitively orders them according to their consistency level:rlx  $\sqsubseteq$  acq  $\sqsubseteq$  acqrel and rlx  $\sqsubseteq$  rel  $\sqsubseteq$  acqrel. Additionally, the cas( $x, e_1, e_2, o_U, o_R$ ) operation atomically updates the location  $\ell$  bound to x to the evaluation of  $e_2$  if  $e_1$  evaluates to the value stored in  $\ell$ , returning true in this case, and returns false otherwise.

The semantics of library implementations are defined in terms of a most general client which can call arbitrary methods in any arbitrary session. Formally, for a library  $\mathcal{L} \in \mathcal{P}(\mathsf{Method})$ , we define a labeled transition system (LTS),  $\Omega_{\mathcal{L}} = (\Phi, \mathsf{Evt}, \Rightarrow)$ , where  $\Phi$  denotes a set of states,  $\mathsf{Evt}$  denotes a set of events (also used as labels on transitions) and  $\Rightarrow \subseteq \Phi \times \mathsf{Evt} \times \Phi$  defines a transition relation over states and events. We write  $\stackrel{\omega}{\Rightarrow}$  for the relation  $\{\langle s_1, s_2 \rangle \| \langle s_1, \omega, s_2 \rangle \in \Rightarrow\}$ .

Automated Robustness Verification of Concurrent Data Structure Libraries against Relaxed Memory Models 362:9

$$\begin{split} I &\in \mathsf{Invocations} = \mathsf{SessionId} \to (\mathsf{InvkEvt} \cup \{\bot\}) \times (\mathsf{Stmt} \cup \{\bot\}) \\ \varrho &\in \mathsf{Environments} = \mathsf{SessionId} \to \mathsf{EnvLocal} \\ \mathcal{L} &\in \mathsf{Library} \in \mathcal{P}(\mathsf{Method}) \end{split}$$

$\rho \in EnvLocal = Var \rightarrow Value$

$I(\tau) = \langle \gamma, \operatorname{return}(e); s \rangle$

$\langle \varrho, I \rangle \xrightarrow{\epsilon} \langle \varrho', I' \rangle$

Ret  $I(\tau) = (\_, \bot) \quad m = \lambda x.s \in \mathcal{L}$  $\varrho' = \varrho \left[ \tau \mapsto \varrho(\tau) \left[ x \mapsto v_a \right] \right]$  $\gamma = \text{Invk}\langle \_, \_, \_, v_r, \tau \rangle \quad e \leadsto_{\varrho(\tau)} v_r$ *i* unique  $\gamma = \text{Invk}\langle i, m, v_a, v_r, \tau \rangle$  $I' = I \left[ \tau \mapsto \langle \gamma, \bot \rangle \right] \quad \varrho' = \varrho \left[ \tau \mapsto \rho_{\bot} \right]$  $I' = I[\tau \mapsto \langle \gamma, s \rangle]$

$\langle \rho, I \rangle \xrightarrow{\gamma} \langle \rho', I' \rangle$

StepLocal

Invk

$$\frac{I(\tau) = \langle \gamma, s \rangle \quad \langle \varrho(\tau), s \rangle \stackrel{\epsilon}{\longrightarrow}_{\tau} \langle \rho', s' \rangle}{I' = I[\tau \mapsto \langle \gamma, s' \rangle] \quad \varrho' = \varrho[\varrho(\tau) \mapsto \rho']} \qquad I(\tau) = \langle \gamma, s \rangle \quad \langle \varrho(\tau), s \rangle \stackrel{\alpha}{\longrightarrow}_{\tau} \langle \rho', s' \rangle}{I' = I[\tau \mapsto \langle \gamma, s' \rangle]} \\

\frac{I(\tau) = \langle \gamma, s \rangle \quad \langle \varphi(\tau), s \rangle \stackrel{\alpha}{\longrightarrow}_{\tau} \langle \rho', s' \rangle}{\langle \varphi, I \rangle} \qquad (\varphi, I) \stackrel{\text{Sil}(\gamma)}{\longrightarrow} \langle \varrho', I' \rangle \qquad (\varphi, I) \stackrel{\mu}{\longrightarrow} \langle \varrho', I' \rangle$$

**StepMem**

#### Fig. 6. Global Reduction Rules

A state in  $\Phi$  is a tuple, comprising a set of thread-local environments ( $\rho$ ) indexed by session ids and a set of current invocations (I, also indexed by session ids) that records the state of each session along with the invocation event of the method currently executing in that session. In an invocation event,  $\ln v \langle i, m, v_a, v_r, \tau \rangle$ , *i* represents an invocation number (a unique identifier for a particular invocation), m is a method name,  $v_a$  and  $v_r$  represent the argument supplied to and value returned by the method, and  $\tau$  is a session identifier. The prophesied return value  $v_r$  must match the value yielded by *e* in any return *e* statement executed during the execution of *m* with invocation number *i*. This follows the convention introduced by [49] to describe method invocations in a relaxed memory setting using a single event, instead of the traditional invocation and response events used in the SC setting.

We note that SessionId is an unbounded set of sessions. The *initial* state  $s_{\perp}$  of  $\Omega_L$  is  $\langle \varrho_{\perp}, I_{\perp} \rangle$ .  $I_{\perp}$ maps each session in SessionId to  $\langle \perp, \perp \rangle$ , while  $\varrho_{\perp}$  maps each variable to an initial value.

Figure 6 defines the semantics of clients. It models the behavior of a most-general client. A client can invoke a new method using the INVK rule, which also establishes an initial local environment. Notice that  $I(\tau) = (\_, \bot)$  ensures that  $\tau$  is not an active session. The RET rule corresponds to the return of a method. We use the notation  $e \sim_{\rho(\tau)} v_r$  to indicate that the expression *e* evaluate to  $v_r$ under the local environment  $\rho(\tau)$ . Notice that the RET rule sets the second component of  $I(\tau)$  to  $\perp$ , thus allowing future calls in  $\tau$  through INVK. The STEP rules allow a method invocation active in a session to take either a silent step (STEPLOCAL) or a step that affects memory (STEPMEM)<sup>1</sup>.

Steps taken by an invocation that do not access shared memory are recorded using a silent event (Sil $\langle \gamma \rangle$ ). Steps that involve either reading or writing from shared memory are recorded using memory events that are of the form: Mem $(i, \tau, \alpha)$ , where *i* is a unique event identifier,  $\tau$  is the session containing the event, and  $\alpha$  defines the particular operation performed on the memory (read (R), write (W), read-modify-update (U), or fence (F)). We assume the language modeled by the LTS is receptive [51] and does not constrain the specific values read from memory. This assumption is consistent with prior work [43] that also separates out the memory system from the program semantics, by allowing load operations to read arbitrary values from memory. These values are then constrained by the memory system as defined in §3.2.

<sup>&</sup>lt;sup>1</sup>The local reduction rules defining  $\xrightarrow{\alpha}_{\tau}$  are straightforward and provided in the appendix, §A.

## 3.2 Memory system

We use declarative specifications of the RC20 memory model to construct the memory system. These specifications constrain *execution graphs*, which consist of the memory events that we defined in the previous subsection, along with a number of binary relations among these events. Formally, an execution graph  $G = \langle M, rf, mo, so \rangle$  consists of a set of memory events M along with the binary relations reads-from (rf), modification-order (mo) and session-order (so). Our development closely follows prior work in this area [33, 38, 43].

*Notation.* For a relation *R*, we write  $R^2$  for the reflexive and  $R^+$  for the transitive closure of *R*,  $R^{-1}$  denotes its inverse, while dom(R) denotes its domain.  $R_1$ ;  $R_2$  denotes the composition of the two relations  $R_1$  and  $R_2$ . Given a set of memory events M, [M] denotes the identity relation on M. Hence,  $[M_1]$ ; R;  $[M_2]$  denotes  $R \cap (M_1 \times M_2)$ . Given an execution graph  $G = \langle M, \text{rf}, \text{mo, so} \rangle$ , we use the notation *G*.*X* to denote the subcomponent *X* of *G*. Given a subset of events  $M' \subseteq G.M$  and binary relation G.R over G.M, we write  $G.R_{|M'}$  to denote the projection of R over the events in M'. We also use the notation  $G.M_{\tau}$  to denote the set of events in G.M of session  $\tau$ , and use  $G.M_{T}$  to denote set of events in G.M of memory event type T (T  $\in$  {R, W, U, F}). We use G.M<sub>W+U</sub> to indicate the set of all write and update events.  $G.M_{\Box X}$  is used to denote the set of all events in G.M whose access mode is related by the partial order  $\sqsubseteq$ , with X. G.M<sub>l</sub> for location l denotes the set of memory events accessing  $\ell$ . We can also combine these notations to denote subsets of events satisfying multiple properties, for example,  $G.M_{W,\ell}$  denotes write events to location  $\ell$ . We use  $G.w_{\ell}^{max}$  to denote the most recent write (or update) event in G.M to  $\ell$  according to the G.m order. Given a memory event  $\mu = \text{Mem}(i, \tau, \alpha)$ , we use various projection functions  $\text{sess}(\mu)$ ,  $\text{type}(\mu)$ ,  $\text{loc}(\mu)$ ,  $\text{rval}(\mu)$ ,  $\text{wval}(\mu)$ ,  $mod(\mu)$  to denote the session, memory event type, memory location, read value, write value, access mode respectively. Similarly, for an invocation event  $\gamma$ , we use functions method( $\gamma$ ), arg( $\gamma$ ), ret( $\gamma$ ) to denote the method name, argument, and return value resp. Given a relation *R* between memory events, we use the notation  $\mu_1 \xrightarrow{R} \mu_2$  to denote  $R(\mu_1, \mu_2)$  for memory events  $\mu_1, \mu_2$ .

*Execution Graphs.* A valid execution graph  $G = \langle M, rf, mo, so \rangle$  obeys certain well-formedness constraints, irrespective of the memory model. These well-formedness constraints follow directly from the definition of the various relations and include the following: (i) mo  $\subseteq M_{W+U} \times M_{W+U}$  is a total order between write/update events to the same location, (ii) so is a total order between events in the same session, (iii) rf  $\subseteq M_{W+U} \times M_{U+R}$  is total on its co-domain and only relates events to the same location and (iv) if  $\mu_1 \xrightarrow{\text{rf}} \mu_2$ , then wval $(\mu_1) = \text{rval}(\mu_2)$ . We denote these constraints by  $\chi_{\text{base}}$ . In order to understand how execution graphs are constrained by memory models, we first describe the specification for SC. Given an execution graph  $G = \langle M, rf, mo, so \rangle$ , we define the following

derived relations:

$$G.fr = (G.rf^{-1}; G.mo) \setminus [G.M] \qquad G.sw = [G.M_{\exists rel}]; ([G.M_F]; G.so)^{?}; G.rf^{+}; (G.so; [G.M_F])^{?}; [G.M_{\exists acq}]$$

$$G.hb_{SC} = (G.rf \cup G.mo \cup G.fr \cup G.so)^{+} \qquad G.hb = (G.sw \cup G.so)^{+}$$

The fr relation relates a read event with write events that it does not witness. Execution graph G is said to be SC-consistent if  $hb_{SC}$  is irreflexive. The  $hb_{SC}$  ordering is an interleaving of events across sessions; making it irreflexive ensures that each read event reads from the most recent write event, formalizing our intuitive understanding of SC executions. We denote this constraint by  $\chi_{sc}(G)$ .

The sw relation relates rel writes with acq reads that read from them, as well as rel and acq fences that have rf-related write and read events between them; hb then transitively expands sw while also taking into account so. An execution graph G is said to be RC20-consistent if the following conditions hold: (1) G.fr; (G.rf)<sup>?</sup>; G.hb is irreflexive; (2) G.mo; (G.rf)<sup>?</sup>; (G.hb)<sup>?</sup> is irreflexive; (3) *G*.fr; *G*.mo is irreflexive; and, (4) *G*.rf  $\cup$  *G*.so is acyclic.

We denote this set of constraints by  $\chi_{RC20}(G)$ . Intuitively, the first two irreflexivity constraints guarantee that read and write operations obey hb ordering, i.e. a read event cannot overlook a write event that *happens-before* the read, and the modification order between two write events must agree with the *happens-before* order. The third irreflexivity constraint guarantees CAS semantics, i.e., two distinct update events cannot read from the same write event. The last constraint is required to prohibit out-of-thin-air reads [9]. Notice that  $\chi_{SC}(G) \Rightarrow \chi_{RC20}(G)$ , and hence, if an execution graph is SC-consistent, it is also RC20-consistent. The above specification of RC20-consistency matches with the development used in previous work [43].

*Traces.* We now present the memory systems for the SC and RC20 memory models. We define a common parameterized system that can be instantiated with either  $\chi_{SC}$  or  $\chi_{RC20}$ . The labeled transition system for memory model X is given by  $\mathcal{MS}_X = \langle \mathcal{G}, \mathsf{MemEvt}, \rightarrow_X \rangle$ . Here,  $\mathcal{G}$  is the set of all execution graphs, MemEvt are memory events as defined earlier, and  $\rightarrow_X \subseteq \mathcal{G} \times \mathsf{MemEvt} \times \mathcal{G}$ are labeled transitions. We define an initial execution graph  $G_{\perp} = \langle M_{\perp}, \emptyset, \emptyset, \emptyset \rangle$ , where  $M_{\perp}$  contains an initial write event  $\mathbb{W} \langle \ell, v_{\ell}^{\perp}, r \mathbf{1}_X \rangle$  to every location  $\ell$ .

Each transition adds a new memory event, corresponding to an arbitrary action  $\alpha$  in arbitrary session  $\tau$ , as long as the new execution graph obeys the well-formedness constraints and the consistency constraints of the memory model. We now take the product of the program semantics  $(\Omega_{\mathcal{L}})$  and memory system  $(\mathcal{MS}_X)$  to describe executions of a library implementation  $\mathcal{L}$  under memory model X. In the product, the transition of the program semantics  $\stackrel{\mu}{\Longrightarrow}$  and the transition of

the memory system  $\xrightarrow{\mu}_X$  must agree on the memory event. For method invocations, returns, or silent transitions of the program semantics, there will be no transitions in the memory system. A *trace* of the combined transition system begins from the initial state  $\langle s_{\perp}, G_{\perp} \rangle$  and contains a finite number of transitions. A *complete trace* must end in a final state  $\langle s_{\perp}, G_{\perp} \rangle \xrightarrow{\omega_1} \dots \xrightarrow{\omega_n} \langle s, G \rangle$ , where in the state *s*, all invocations have completed their executions, i.e. there are no pending return statements in any session.

In the following, we consider an execution of a library implementation L under memory model X to be a tuple  $E = \langle t, \Gamma, G \rangle$  where t is a trace of the combined transition system  $\Omega_L \times \mathcal{MS}_X$ ,  $\Gamma$  is the set of all method invocation events and G is the execution graph in the final state of the trace. We also define an invocation session order so<sub>inv</sub>, which relates invocation events belonging to the same session in the order in which they appear in the trace t. We use the notation  $\mathcal{E}_X^L$  to denote the set of all such executions. Similarly, a complete execution corresponds to a complete trace, and we use  $\mathcal{CE}_X^L$  to denote the set of all complete executions. We also use the notation E.G to denote the execution graph of E, and E.M, E.rf, E.mo, E.so to denote the various components of the execution graph G.

# 3.3 Robustness and Library Correctness under SC

The robustness problem, in general, asks whether every RC20 execution of a program is also possible under SC. In the context of library implementations, we re-define the notion of execution-graph robustness, originally proposed in [38], as follows:

Definition 3.1. An execution  $E \in \mathcal{E}_{\mathsf{RC20}}^L$  of a library implementation *L* is *execution-graph robust*, if  $E \in \mathcal{E}_{\mathsf{SC}}^L$ . A library implementation *L* is execution-graph robust if all of its complete executions  $E \in \mathcal{CE}_{\mathsf{RC20}}^L$  are execution-graph robust.

Our verification strategy (described in §4) uses the SC specification of a library implementation to discharge the verification conditions. The correctness of a library implementation under SC is typically specified using the notion of linearizability, which tries to establish a simulation between concurrent executions of the implementation and sequential executions of a reference implementation of the same data structure. However, previous works ([23, 25]) have also proposed

alternative declarative specifications which are equivalent to linearizability and which directly constrain the argument/return value of invocations using a collection of axioms. Such a declarative specification is more amenable to SMT encoding, and hence we have used such specifications in our work. The specifications also establish a *happens-before* ordering among invocations (hb<sub>inv</sub>) which is required to be a total order.

For example, to provide a declarative specification of the register library of Fig. 2, we first define a binary predicate match over invocation events in an execution, which is used in the following three specification predicates. These take as input the invocation events  $\Gamma$  in an execution *E* of the library implementation:

| $match(\gamma_1, \gamma_2)$      | ≜ | $method(\gamma_1) = set \land method(\gamma_2) = get \land arg(\gamma_1) = ret(\gamma_2)$                                                                                                                      |

|----------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\chi_{\text{GetSet}}(\Gamma)$   | ≜ | $\forall \gamma \in \Gamma. \ method(\gamma) = get \land ret(\gamma) \neq UNDEF \Rightarrow \exists \gamma' \in \Gamma. \ match(\gamma', \gamma) \land$                                                        |

|                                  |   | $\gamma' \xrightarrow{hb_{inv}} \gamma$                                                                                                                                                                        |

| $\chi_{\text{GetFrom}}(\Gamma)$  | ≜ | $\forall \gamma_1, \gamma_2, \gamma_3 \in \Gamma. \neg (match(\gamma_1, \gamma_2) \land method(\gamma_3) = set \land \gamma_1 \xrightarrow{hb_{inv}} \gamma_3 \land \gamma_3 \xrightarrow{hb_{inv}} \gamma_2)$ |

| $\chi_{\text{GetUNDEF}}(\Gamma)$ |   | $\forall \gamma_1, \gamma_2 \in \Gamma. \text{ method}(\gamma_1) = \texttt{set} \land \texttt{method}(\gamma_2) = \texttt{get} \land \gamma_1 \xrightarrow{\texttt{hb}_{inv}} \gamma_2$                        |

|                                  |   | $\Rightarrow \operatorname{ret}(\gamma_2) \neq UNDEF$                                                                                                                                                          |

| χlin                             | ≜ | $(so_{inv} \Rightarrow hb_{inv}) \land hb_{inv}$ is a total order                                                                                                                                              |

$\chi_{\text{GetSET}}$  constrains all get invocations that return non-UNDEF values to match their return values with the argument value of some set invocation (and also defines hb<sub>inv</sub> relation between them),  $\chi_{\text{GetFRoM}}$  disallows scenarios in which a get invocation returns the value of an older (not mostrecent) set operation, while  $\chi_{\text{GetUNDEF}}$  disallows a get operation to return UNDEF if there is set operation before it.  $\chi_{\text{LIN}}$  ensures that hb<sub>inv</sub> is a total order and obeys the session order among invocations. The set  $\chi_{\text{Reg}} = {\chi_{\text{GetSet}}, \chi_{\text{GetTRoM}}, \chi_{\text{GetUNDEF}}, \chi_{\text{LIN}}}$  defines a specification of the register library equivalent to linearizability[25]. Under SC, it is easy to see that any execution of the implementation of Fig. 2 satisfies  $\chi_{\text{Reg}}$ .

In general, given a library implementation  $\mathcal{L}$  of data structure  $\mathcal{D}$  with specification  $\chi_{\mathcal{D}}$ , we assume library correctness under SC, which means that every complete execution  $E = \langle t, \Gamma, G \rangle \in C\mathcal{E}_{SC}^{L}$  satisfies the specification, i.e.  $\mathcal{A}_{i}(\Gamma)$  holds for all  $\mathcal{A}_{i} \in \chi_{\mathcal{D}}$ . Declarative specifications equivalent to linearizability have been defined for all common data structures such as stack, queue, set, etc. in previous works [25]. These specifications can be easily encoded as FOL formulae over the domain of invocation events, constraining the method names, arguments, return value and the session order relation. Note that specifications do not directly constrain any internal event of the library implementation, since these would not be directly observable to a client, and the specification should be agnostic of the implementation.

#### 4 Induction for Robustness

In this section, we adapt an existing approach [43] to checking robustness of programs under the RC20 memory model to the library setting, and in particular derive an inductive strategy for establishing robustness. Our strategy is based on deriving sufficient conditions for robustness, such that if these conditions are maintained at every step in every SC execution of the implementation, then it is guaranteed to be execution-graph robust. In order to describe this robustness condition, we first define the notion of prefix of executions.

Definition 4.1. Given a complete execution  $E = \langle t, \Gamma, G \rangle \in C\mathcal{E}_{SC}^L$  of implementation L under SC, a prefix  $E' = \langle t', \Gamma', G' \rangle \in \mathcal{E}_{SC}^L$  is an execution obtained from a prefix t' of the trace t. That is, there exists t'' such that  $t = t' \circ t''$  where  $\circ$  composes two traces if the final state in t' is the same as the initial state of t''.

Note that for every relation R defined in the execution graph G, the relation R' in the execution graph G' will be  $R_{|G'.M}$ . That is because for events  $e_1, e_2 \in G'.M$ , if  $e_1 \xrightarrow{R} e_2$ , then since both events also occur in the trace t', we would also have  $e_1 \xrightarrow{R'} e_2$ . The prefix E' also obeys the following property:

$$\forall \mu' \in E'.M. \ \forall \mu \in E.M. \ \mu \xrightarrow{E.so} \mu' \Longrightarrow \mu \in E'.M$$

That is, if an event  $\mu'$  is in the prefix, then every event  $\mu$  before it in the same session must also be in the prefix. We now define the next event of a prefix:

Definition 4.2. Given a prefix  $E' = \langle t', \Gamma', G' \rangle$  of  $E, \mu$  is called the next event of E' if  $t' \xrightarrow{\omega_1} C_1 \xrightarrow{\omega_2} C_2 \Rightarrow \dots \xrightarrow{\omega_{n-1}} C_{n-1} \xrightarrow{\mu} C_n$  is also a prefix of t, where  $\omega_1, \dots, \omega_{n-1}$  are either invocation events or local events and  $\mu$  is a memory event.

The next event of prefix E' is denoted by next(E', E). For prefix E' and  $\mu = next(E', E)$ ,  $E' + \mu$  is used to denote the execution corresponding to the prefix of E ending in event  $\mu$ . The following definition characterizes a non-robustness witness[43], i.e. a SC execution which leads to a non-robust RC20 execution.

Definition 4.3. Given a complete SC execution  $E \in C\mathcal{E}_{SC}^{L}$  of implementation *L*, let *E'* be a prefix of *E* and event  $\mu = \text{next}(E', E)$  such that  $\text{loc}(\mu) = \ell$  and  $\text{sess}(\mu) = \tau$ . Then *E'* is a non-robustness witness if the following conditions are true:<sup>2</sup>

- (1)  $E'.w_{\ell}^{\max} \in dom(E'.hb_{SC}^?; [E'.M_{\tau}])$

- (2) There exists  $\mu_{w} \in E'.M_{w,\ell} \cup E'.M_{U,\ell}$  such that  $\mu_{w} \neq E'.w_{\ell}^{\max}$ ,  $\mu_{w} \notin dom(E'.mo;E'.rf^{?};E'.hb^{?};[E'.M_{\tau}])$  and if  $act(\mu) \neq R$  then  $\mu_{w} \notin dom(E'.rf;[E'.M_{U}]))$  and

The non-robustness witness definition formalizes our intuitive understanding of a non-robust execution: for a prefix E', the next event  $\mu$  can be non-robust (i.e. can have a different behavior under RC20 and SC memory models) if the most recent write event  $w_{\ell}^{\text{max}}$  to  $\ell$  occurs hb<sub>SC</sub>-before the session containing  $\mu$ , so under SC, if  $\mu$  is a read event, then it must read from  $w_{\ell}^{\text{max}}$ . But  $w_{\ell}^{\text{max}}$  does not occur hb-before the session containing  $\mu$  (because of the presence of the earlier write event  $\mu_w$ ), so that in a RC20 execution,  $\mu$  can read from  $\mu_w$ . Note that if  $\mu$  is not a read event, then the definition further constrains the earlier write event  $\mu_w$  to not be related by rf to an update event, since the CAS semantics even under the C11 memory model would not allow another write (in this case  $\mu$ ) to come between the write ( $\mu_w$ ) from which an update events reads from. In essence, referring back to the memory system defined in Sec. 3.2,  $E'.G \xrightarrow{\mu}_{\text{RC20}} E'.G + \mu$  would be a valid transition in the RC20 memory model, but this would not be a valid transition in the SC system.

Further, the execution leading up to such a non-robustness witness must obey SC semantics, thus characterizing the first (or minimal) violation of robustness. If we can ensure such a non-robustness witness does not arise during any SC execution, the library implementation is guaranteed to be robust.

THEOREM 4.4. Given a library implementation L, if every prefix E' of every complete execution  $E \in C\mathcal{E}_{SC}^{L}$  is not a non-robustness witness, then L is execution-graph robust<sup>3</sup>.

The above theorem is a direct application of Theorem 4.6 in [43] but applied to executions of a library implementation in the presence of the most general client. In order to illustrate this idea,

<sup>&</sup>lt;sup>2</sup>Adapted from Definition 4.5 in [43]

<sup>&</sup>lt;sup>3</sup>All proofs can be found in appendix, §B

we revisit the execution in Figure 3. Notice that just before the event  $R(N \rightarrow val, v, rlx)$ , the most recent write event to the location  $N \rightarrow val$ ,  $W(N \rightarrow val, v, rlx)$ , is in both  $hb_{SC}$  and hb order, thus ensuring that the read event has the same behavior under both SC and RC20. On the other hand, suppose we modified the library implementation and changed the access modes of either the load or store of L to be rlx. Then, we would get a non-robustness witness E' consisting of the two events of the set invocation (on the left) and the first event of the get invocation (R(L,N,rlx)), with the next event being the read of  $N \rightarrow val$ . This witness can be obtained through an SC execution, in the sense that it does not violate  $\chi_{SC}$ , and it obeys both the conditions of Definition 4.3. In particular, with the next event to E' being a read to location  $N \rightarrow val$ , the most recent write event  $w_{N\rightarrow val}^{max}$  is  $W(N \rightarrow val, v, rlx)$  and it is in  $hb_{SC}$  order to the session on the right (thus obeying condition-1), but it is not in hb order to it. As a result, the initializing write event to  $N \rightarrow val$  (not depicted in the figure) would take the role of the event  $\mu_w$  in condition-2 of Definition 4.3. Hence, relaxing the access mode of either of the accesses to the location L renders the library implementation non-robust.

While Definition 4.3 simplifies our task of proving robustness of executions by reducing it to a search problem over SC executions, this is still a tall order, as it requires maintaining information about relations between low-level events across an unbounded number of arbitrarily long executions involving an unbounded number of heap locations. To address this issue, our verification strategy uses induction on the prefixes of SC executions, and then shows the absence of a non-robustness witness at every step of every SC execution. We can try to use the non-existence of a non-robustness witness itself as an inductive invariant. That is, for an SC execution *E*, we consider a prefix *E'* and assume inductively that for  $\mu = \text{next}(E', E)$ , *E'* and  $\mu$  do not form a non-robustness witness. Notice from Def. 4.3 that *E'* and  $\mu$  not forming a non-robustness witness would mean  $\neg((1) \land (2)) \equiv (1) \Rightarrow \neg(2)$ , which essentially means that if *E'*.w<sub>\ell</sub><sup>max</sup> is in hb<sub>SC</sub> order before session  $\tau$ , then it should also be in hb order before  $\tau$ .

Unfortunately, we find that this does not constitute an appropriate inductive invariant, since it only constrains the events that access location  $\ell$ , but the next event of the new prefix  $E' + \mu$  may access a different location after this event is added. Hence, the inductive hypothesis involving  $\ell$  is not useful. We could try to use as inductive invariant the required property for all locations: i.e.  $\forall \ell$ , if  $E' . w_{\ell}^{max}$  is in hb<sub>SC</sub> order before some session  $\tau$ , it is in hb order before it. However, this condition is too strong and not necessary for establishing non-robustness. This is because even if this condition does not hold for some location (say  $\ell'$ ), which means that  $E' . w_{\ell}^{max}$  is in hb<sub>SC</sub> order before it, the next event in  $\tau$  must access  $\ell'$  to form the actual non-robustness witness. The presence of such a event  $E' . w_{\ell}^{max}$  is a necessary condition for forming an actual non-robustness witness, which we formalize below as a potential witness:

Definition 4.5. Given an execution  $E \in C\mathcal{E}_{SC}^{L}$ , a prefix E' of  $E, \mu \in E'.M$  and a write event  $\mu' \in E'.M_{W}^{\max} \cup E'.M_{U}^{\max}, E', \mu'$  and  $\mu$  form a potential non-robustness witness if  $\mu' \xrightarrow{E'.hb_{SC}} \mu$  and  $\neg(\mu' \xrightarrow{E'.hb} \mu)$ .

$E.M_{W}^{max}$  indicates the set of maximal events in *E* according to the mo ordering. Note that to obtain an actual non-robustness witness, we would have to instantiate the above definition with  $\mu' = w_{\ell}^{max}$  for some location  $\ell$ , and the next event in the session containing  $\mu$  must also access  $\ell$ . Figure 7 shows a potential non-robustness witness for the register library implementation. It shows an execution with two set invocations which happen in different sessions. Because of the mo relation between the two write events to location L, the write event  $W(N_1 \rightarrow val, v_1, rlx)$  comes in hb<sub>SC</sub> order to the last event of session  $\tau_2$  ( $W(L, N_2, rel )$ ), but it is not in hb order before

it. Using the notation of the above definition, E' would be the execution depicted in Figure 7,  $\mu'$  would be the write event to N<sub>1</sub>  $\rightarrow$  val, and  $\mu$  would be the write event to L in session  $\tau_2$ .

A potential non-robustness witness, consisting of prefix E' and the write event  $\mu'$  can become an actual non-robustness witness if E' can be expanded into another prefix E'' such that the next event  $\mu''$  of E'' accesses the location of  $\mu'$ ,  $\mu'$  continues to remain the most recent write to its location, and the non-hb hb<sub>SC</sub> relation continues to exist between  $\mu_w$  and  $\mu''$ . For the potential non-robustness witness of Fig. 7, a

Fig. 7. Potential non-robustness witness in the register library implementation.

subsequent immediate access to location  $N_1 \rightarrow val$  would result in an actual non-robustness witness. While every potential witness does not necessarily become an actual witness, an actual witness must have been at some stage a potential witness. For example, the potential non-robustness witness in our example will never result in an actual witness, since there will be no further access to the location  $N_1 \rightarrow val$  in an SC execution. Intuitively, this is because of the register semantics, as the effect of a set invocation  $\gamma_2$  "overwrites" the effects of a previous set invocation  $\gamma_1$  through the write to location L, and the  $\chi_{GetFROM}$  specification prohibits a get invocation to read from an older set invocation.

Table 1. Sufficient conditions for establishing robustness inductively.

| $\Phi_{src}(E, \ell)$           | $\forall \mu_m \in E.M_{\mathbb{W}}^{\max} \cup E.M_{\mathbb{U}}^{\max}. \ \forall \mu_1, \mu_2 \in E.M. \ loc(\mu_m) = \ell \land$                                                                                                                           |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | $\wedge \mu_m \xrightarrow{E.\text{hb}^2} \mu_1 \wedge \mu_1 \xrightarrow{E.\text{fr} \vee E.\text{mo} \vee E.\text{rf}} \mu_2 \Longrightarrow \exists \mu_3 \in E.M. \ \mu_m \xrightarrow{E.\text{hb}} \mu_3 \wedge \mu_3 \xrightarrow{E.\text{hb}^2} \mu_2$ |

| $\overline{\Phi_{dst}(E,\ell)}$ | $\forall \mu_m \in E.M_{W}^{max} \cup E.M_{U}^{max}. \forall \mu_1, \mu_2 \in E.M. \operatorname{loc}(\mu_m) = \ell \wedge \operatorname{loc}(\mu_2) = \ell$                                                                                                  |

|                                 | $\wedge \mu_m \xrightarrow{E.\text{hb}_{SC}} \mu_1 \wedge \mu_1 \xrightarrow{E.\text{so}} \mu_2 \Rightarrow \exists \mu_3 \in E.M. \ \mu_m \xrightarrow{E.\text{hb}} \mu_3 \wedge \mu_3 \xrightarrow{E.\text{so}} \mu_2$                                      |

In order to verify robustness, we then have to ensure that either a potential non-robustness witness is not formed at all (thus ensuring robustness at the source), or if a potential robustness witness does form, it does not manifest into an actual non-robustness witness (thus ensuring robustness at the destination). As shown in Table 1, we present two conditions ( $\Phi_{src}$  and  $\Phi_{dst}$ ) that ensure the absence of a non-robustness witness by disallowing it at the source and destination, resp. These conditions are parametric on executions and locations.

We first focus on  $\Phi_{src}$ , which inductively tries to maintain the non-existence of a potential non-robustness witness. In order to understand  $\Phi_{src}(E, \ell)$ , we note that the only difference between the definitions of hb and hb<sub>SC</sub> is that the rf relation between relaxed accesses as well as fr and mo relations between any two accesses induce an hb<sub>SC</sub> relation, but they do not induce an hb relation. Hence, whenever hb<sub>SC</sub> is established due to these relations, we should also be able to establish hb.  $\Phi_{src}$  considers a maximal write event  $\mu_w$  to location  $\ell$  in *E*. If there exists a hb<sub>SC</sub> (and hence inductively hb) relation from  $\mu_w$  to some event  $\mu_1$ , and if this hb<sub>SC</sub> relation were to be extended to  $\mu_2$  by a fr, mo or rf relation between  $\mu_1$  and  $\mu_2$ , then there should also exist a hb relation from  $\mu_w$  to  $\mu_2$ , through some event  $\mu_3$ . To illustrate, we refer back to Figure 4, which essentially shows the different cases to be handled in order to establish  $\Phi_{src}(E, L)$  for every SC execution *E* of the register implementation. In particular, for the case depicted in Figure 4(a), using the notation of  $\Phi_{src}$ ,  $\mu_w = \mu_1 = W \langle L, \_, rel \rangle$  and  $\mu_2 = \mu_3 = R \langle L, \_, acq \rangle$ . Cases depicted in Figure 4(b)-(d) do not satisfy the antecedent of  $\Phi_{src}$  (because there does not exist events  $\mu_1, \mu_2$  with the required relation between them), while for the case depicted in Figure 4(e),  $\mu_1 = W \langle N \rightarrow val, \_, \rangle$ ,  $\mu_2 = R \langle N \rightarrow val, \_, \rangle$ ,

and  $\mu_3 = \mathsf{R}\langle \mathsf{L}, \mathsf{N}, \mathsf{acq} \rangle$ ;  $\mu_3$  is not depicted in the figure, but it would occur before  $\mu_2$  in the same get invocation. Note that the antecedent of  $\Phi_{src}$  simply means that  $\mu_w \xrightarrow{\mathsf{hb}} \mu_2$ , but explicitly maintaining the event  $\mu_3$  which establishes this hb relation helps us in the SMT encoding of  $\Phi_{src}$ , as we will explain in the next section.

Now, if  $\Phi_{src}$  cannot be established, then a potential non-robustness witness may be formed, as illustrated in Fig. 7. Notice that this means that  $\Phi_{src}(E, N_1 \rightarrow val)$  does not hold for the execution E of Fig. 7. Then, we use the condition  $\Phi_{dst}$  to prevent such a potential non-robustness witness from turning into an actual witness. In words, this condition considers a scenario when there is a maximal write event  $\mu_w^{max}$  to location  $\ell$  which occurs hb<sub>SC</sub>-before event  $\mu_1$ , with a later event  $\mu_2$  in the same session accessing the location  $\ell$ . This could lead to an actual non-robustness witness, with the prefix being the execution corresponding to the trace leading upto the state just before  $\mu_2$ . However, in such a scenario,  $\Phi_{dst}$  enforces the existence of another event  $\mu_3$  before  $\mu_2$  ( $\mu_3$  could be the same as  $\mu_1$ ) in the same session, such that  $\mu_w^{max}$  occurs hb-before  $\mu_3$ . This would prevent the formation of an actual non-robustness witness involving  $\mu_w^{max}$  and  $\mu_2$ .

To illustrate, we have already established through Fig. 7 that  $\Phi_{src}$  does not hold for the location  $N_1 \rightarrow val$ . To show  $\Phi_{dst}$ , we let  $\mu_w$  be  $W(N_1 \rightarrow val, v_1, rlx)$ , while  $\mu_1$  would be some event which occurs in so-order before  $\mu_2$ , which has to be another access to  $N_1 \rightarrow val$ . As per the program structure of the register library,  $\mu_2$  can only be a read event, which must occur in a get invocation. The scenario exactly corresponds to Fig. 3, where, using the notation of  $\Phi_{dst}$ ,  $\mu_w = W(N \rightarrow val, v, rlx)$ ,  $\mu_1 = R(L, N, acq)$  and  $\mu_2 = R(N \rightarrow val, v, rlx)$ . However, in this case,  $\mu_1$  must read from W(L, N, acq), because there is no another write to L which writes N (guaranteed by the malloc semantics). Hence, we can instantiate  $\mu_3$  with  $\mu_1$  itself in the consequent of  $\Phi_{dst}$ .

Notice that if  $\Phi_{src}(E, \ell)$  holds, then  $\Phi_{dst}(E, \ell)$  also holds, because hb<sub>SC</sub> would imply hb from write events to  $\ell$ , in which case we can take  $\mu_3 = \mu_1$ . However, in general,  $\Phi_{dst}$  does not imply  $\Phi_{src}$  (as we saw for the location N<sub>1</sub>  $\rightarrow$  val). The reason we separate out the two conditions is because for some locations, it is easier to establish  $\Phi_{src}(E, \ell)$ , since the condition just requires one access to the location  $\ell$ , as opposed to  $\Phi_{dst}(E, \ell)$  which requires two accesses. The distinction will become more clear when we go through our SMT encoding in §7.

To summarize,  $\Phi_{src}(E, \ell)$  prevents the formation of a potential non-robustness witness involving location  $\ell$ , while  $\Phi_{dst}(E, \ell)$  prevents a potential non-robustness witness involving  $\ell$  from turning to an actual non-robustness witness. If we can show that  $\forall \ell \in \text{Location}. \forall E \in C\mathcal{E}_{SC}^{L}$ .  $\Phi_{dst}(E, \ell) \lor \Phi_{src}(E, \ell)$ , then we can inductively show execution-graph robustness.

THEOREM 4.6. Given a library implementation L, if  $\forall \ell \in \text{Location}. \forall E \in C\mathcal{E}_{\text{SC}}^L$ .  $\Phi_{dst}(E, \ell) \lor \Phi_{src}(E, \ell)$ , then L is execution-graph robust.

We note that Theorem 4.6 does not hold in the other direction, i.e.  $\Phi_{dst}$  and  $\Phi_{src}$  are not necessary for ensuring execution-graph robustness. In particular, there is a gap between the definition of a non-robustness witness (Def. 4.3) and the conditions  $\Phi_{src}$  and  $\Phi_{dst}$ . These conditions merely ensure that if the maximal write  $\mu_m$  to a location appears hb<sub>SC</sub>-before the next access to it, it also appear hb-before it. They do not consider the non-maximal write  $\mu_w$  from Def. 4.3 at all, which is actually the root cause of the non-robust behavior. In particular, consider the scenario where a non-maximal write  $\mu_w$  may be in rf relation to an update event, and hence cannot cause a robustness violation if the next event (say  $\mu$ ) to be added is a write/update event to the same location as  $\mu_w$ , and the maximal write  $\mu_m$  is in hb<sub>SC</sub> order to the session containing  $\mu$ . In this case, act( $\mu \neq R$ ,  $\mu_w \in dom(E'.rf; [E'.M]_U)$  (here E' is the set of events in the execution, see point(2) in Def. 4.3). Hence, we do not require  $\mu_w$  and consequently  $\mu_m$  to be hb-before  $\mu$ . Fig. 8 concretely demonstrates this scenario. Assume that all the events in the execution come from some library invocations. The update operation to  $\ell_1$  in  $\tau_2$  reads from the write to  $\ell_1$  in  $\tau_1$ . The read in  $\tau_3$  to location  $\ell_2$  reads from the write in  $\tau_2$ , hence the maximal write to  $\ell_1$  (which is the update in  $\tau_2$ ) is in hb<sub>SC</sub> order, but not in hb order to  $\tau_3$ , since the accesses to

| Session $\tau_1$                                                | Session $	au_2$                      | Session $\tau_3$                  |

|-----------------------------------------------------------------|--------------------------------------|-----------------------------------|

| $\texttt{W} \langle  \ell_1, \texttt{1}, \texttt{rlx}  \rangle$ | $U\langle \ell_1, 1, 2, rlx \rangle$ | $R\langle\ell_2,1,rlx\rangle$     |

|                                                                 | $W\langle \ell_2, 1, rlx \rangle$    | $W\langle \ell_1, 3, rlx \rangle$ |

|                                                                 |                                      |                                   |

Fig. 8. Execution illustrating incompleteness of  $\Phi_{src}$  and  $\Phi_{dst}$ .

$\ell_2$  are relaxed. Excluding the write to  $\ell_1$  in  $\tau_3$ , the execution is a potential non-robustness witness. Let E' be this execution, with the next event  $\mu = W\langle \ell_1, 3, r | x \rangle$ . Following the notation used in Def. 4.3, we have the maximal write to  $\ell_1, \mu_m = U\langle \ell_1, 1, 2, r | x, r | x \rangle$ , and a non-maximal write  $\mu_w = W\langle \ell_1, 1, r | x \rangle$ . Now,  $E' + \mu$  is not an actual non-robustness witness, because even though  $\mu_m$  is hb<sub>SC</sub> order and  $\mu_w$  is not in hb order to the session  $\tau_3, \mu_w$  is in rf order to an update event, and hence  $\mu_w$  does not satisfy point(2) of Def. 4.3.

We note that except scenarios like the one given above,  $\Phi_{src}$  and  $\Phi_{dst}$  precisely model the absence of non-robustness witnesses, i.e. if these conditions are violated, it would imply the presence of an actual non-robustness witness. A distinguishing property of executions like Fig. 8 is that they involve at least one update event (generated through CAS operation) to a location. We have observed that in library implementations, either all writes to a location happen through CAS operations, or none do (i.e. it doesn't happen that there is both a CAS and a normal write operation to the same location). If all accesses to a location are through CASes, our automated verification strategy (given in §7) uses additional CAS constraints, which helps us avoid any false positives (like the execution in Fig. 8) arising out of the imprecision of  $\Phi_{src}$  and  $\Phi_{dst}$ .

## 5 Induced Subgraph Robustness

We now discuss the challenges that arise in using our verification strategy on real-world library implementations, and the mechanisms we employ to overcome them.

We observe that the notion of execution-graph robustness is often too strong for real-world library implementations that use low-level synchronization primitives such as compare-and-swap (CAS). A typical CAS-based synchronization pattern is as follows: a method invocation performs a number of speculative reads without any synchronization, followed by some computation based on these speculative reads, and then finally stores the result of this computation to the global state if no other concurrent method invocation has made conflicting changes. The pattern uses CAS operations to determine if a conflict exists. If another concurrent invocation has indeed made changes to the global state, the speculative computation is ignored (since the corresponding CAS would fail), and the pattern is retried. These speculative computations are often performed using relaxed accesses, and they may generate an arbitrary number of read/write events. Any non-robust behavior of such events would result in a failing CAS, in effect restarting the entire invocation. It is clearly ineffective to establish the robustness of events that are generated by such failed computation. A concrete example of a library implementation demonstrating this pattern is given in the supplemental material, §4.

In particular, an RC20 execution of a library implementation may be still be effectively robust against SC even if it exhibits potentially non-robust actions if all events that actually affect the return value of any method invocation obey SC semantics. To capture this distinction, we define a new notion of robustness called *induced subgraph robustness* that only focuses on the robustness of events that actually effect the client observable behavior of an invocation. Given an execution graph  $G = \langle M, \text{rf}, \text{mo}, \text{so} \rangle$ ,  $G' = \langle M', \text{rf}', \text{mo}', \text{so}' \rangle$  is called an induced subgraph of G if  $M' \subseteq M$  and  $\text{rf}' = \text{rf}_{|M'}$ ,  $\text{mo}' = \text{mo}_{|M'}$ ,  $\text{so}' = \text{so}_{|M'}$ .

Definition 5.1. A complete execution  $E = \langle t, \Gamma, G \rangle \in C\mathcal{E}^L_{RC20}$  of a library implementation *L* is *induced subgraph robust* if there exists a complete execution  $E' = \langle t', \Gamma', G' \rangle \in C\mathcal{E}_{SC}^L$  such that (i)  $\Gamma' = \Gamma$ , (ii) For all invocation events  $\gamma_1, \gamma_2 \in \Gamma$ ,  $\gamma_1$  occurs before  $\gamma_2$  in trace  $t \Leftrightarrow \gamma_1$  occurs before  $\gamma_2$  in trace t' and (iii) G' is an induced subgraph of G. L is induced subgraph robust if all of its complete executions  $E \in C\mathcal{E}_{RC20}^{L}$  are induced subgraph robust.